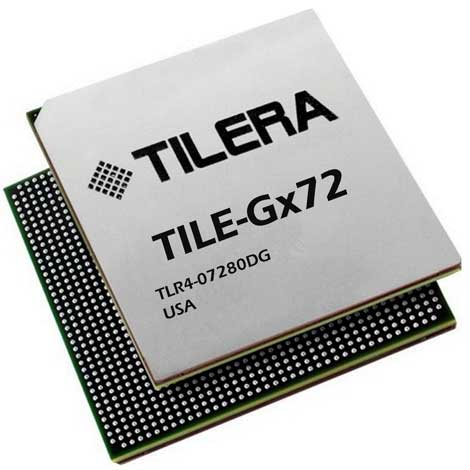

Tilera continues to develop new many-core processors built for the massive data processing needs of "hyper-connected" technology companies. Tilera's newest offering is the GX-72, which boosts the number of cores it can harness to address bottlenecks in networks and applications. The new chip, which is being released today, can be used to power servers or as an accelerator an offload engine for x86-based hardware, an approach that broadens the potential uses for the technology.

The GX-72 is optimized for busting bottlenecks in moving large amounts of data. It builds upon Tilera's architecture, which eliminates the on-chip bus interconnect, a centralized intersection where information flows between processor cores or between cores and the memory and I/O. Instead, Tilera employs an on-chip mesh network to interconnect cores.

The GX-72 is a 64-bit system-on-chip (SoC) equipped with 72 processing cores, 4 DDR memory controllers and a big-time emphasis on I/O. This includes 8 ports for 10 Gb Ethernet, 32 for 1Gb Ethernet, 24 lanes of PCIe 2.0 and Tilera's MICA acceleration engine.

Tilera CEO: "Unprecedented" Compute

"Customers demand ever-increasing levels of performance and performance-per-watt to stay competitive and they simultaneously want to reuse their software and hardware investments across their product portfolio," said Devesh Garg, president and CEO of Tilera. "The TILE-Gx72 brings an unprecedented amount of compute to customer designs, and leverages thousands of open source libraries and the growing Linux ecosystem. The TILE-Gx72 rounds out our processor portfolio, complementing our 9, 16 and 36-core TILE-Gx processors and is offering a remarkable range of processing performance."

Tilera is part of an emerging ecosystem of companies seeking to harnesses thousands of low-power cores that work together on computing tasks. Tilera's processors have proven to be particularly effective in web-scale operations like load balancing, image compression and especially caching, where Facebook has cited Tilera's performance-per-watt in memcached applications.

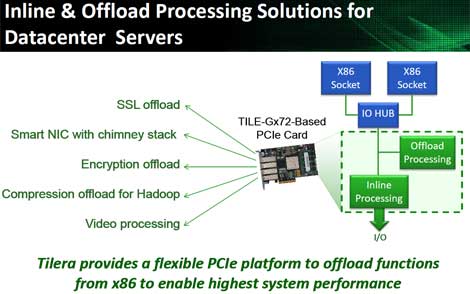

With the GX-72, Tilera is also touting its capabilities as an "offload engine" - a network interface card (NIC) that can plug into an x86 server using a PCIe connection, accelerating data handling by using both the many-core and x86 architectures to process data. One application for this is network monitoring and intrusion detection, allowing rapid inspection of data as it enters a system.

Security Use Cases

"We have a pretty high bar on what we can put on an accelerator," said Bob Doud, the Director of Processor Strategy at Tilera. "It can be used for network intelligence: packet monitoring, visibility into fast-moving traffic, capturing packets and filtering at higher speed."

With more companies moving large volumes of encrypted traffic, that's an important capability. "If 100 percent of your traffic is encrypted, that's a crushing load," said Doud.

"We continue to be impressed with the scalability of the TILE-Gx family with its seamless software compatibility from 9 cores to 72 cores," said Ofer Raz, head of platforms and architecture at security specialist Check Point Software Technologies. "The TILE-Gx72 processor brings the right mix of compute, low-latency I/O, memory bandwidth, and accelerators for the needs of our intelligent, integrated security appliances."

The GX-72 is also proving effective in managing large volumes of video content, either in HTTP streaming or video conferencing. An example: a law enforcement agency using Tilera chips to accelerate processing of incoming video that may need to be quickly redeployed back out to the field.

Here's a slide that offers an overview of Tilera's approach to offload processing and some of the use cases: